无锡芯光互连技术研究院在先进封装设计领率具备丰富的经验,能够支持基板封装设计和晶圆级封装设计。我们会根据客户不同产品的需求,兼顾DFM(design for manufacture)和DFC(design for cost),使产品在成本、性能、良率方面具备竞争力。

随着电子产品朝小型化和集成化的趋势不断发展,如何在有限的空间内放置更多元器件的问题变得越来越重要,研究院通过电、热及应力仿真,优化设计,满足产品的高速率、高密度互连需求。

一、基板封装设计

基板封装通过基板方式实现芯片和下方管脚(如锡球)的互连导通,能够支持FC-BGA、FC-CSP, Chiplet封装设计,最大封装尺寸大于60x60mm,最多线路层数超过20层。

|  |

| FC-BGA基板封装俯视图 | FC-BGA基板封装侧视图 |

二、晶圆级封装设计

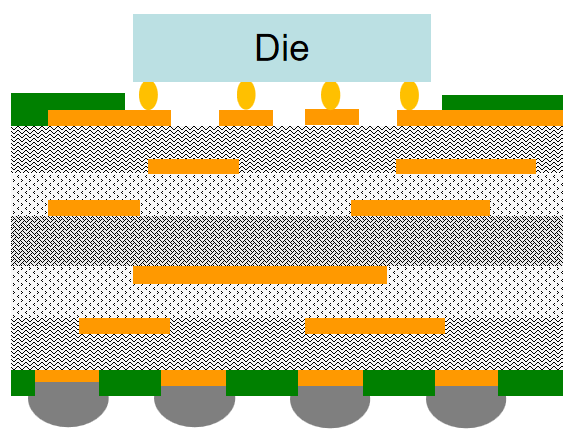

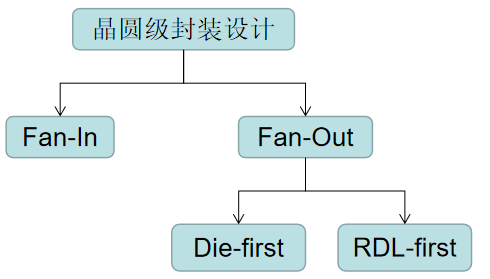

相较于传统基板类封装形式,研究院同样支持晶圆级封装设计,包括Fan-In、Fan-Out。晶圆级封装通过多层RDL布线实现晶圆上多芯片的互连及管脚的引出。

Fan-In主要应用于芯片bump密度低的情况,封装尺寸与芯片尺寸一致。随着bump密度的提升,Fan-Out的使用越来越广泛,封装尺寸大于芯片尺寸。按照RDL及芯片贴装的顺序,Fan-Out可分为Die-first和RDL-first两种不同的工艺路线。RDL线路可支持6L,线宽/线距:2/2um min。

研究院通过RDL-first Fan-Out技术可以实现chiplet封装,chiplet封装设计将面积巨大功能复杂的单芯片或系统(SoC)拆解成不同功能的小芯粒,再利用三维堆叠及RDL的方式重新组合,达到大芯片的功能,具有研发周期短、成本低的特点。

三、仿真

仿真是确保芯片产品性能的重要工具,包括电信号完整性和电源完整性仿真、热及应力仿真,在产品前期开发阶段解决封装设计,加工及使用过程中各种可能碰到的的性能不达标、发热、翘曲等问题。

|

|

|

| 电仿真 | 热仿真 | 应力仿真 |